【华为】verilog语言编写规范 (一)

来自微信公众号 “数字积木”。

1 目的

本规范的目的是提高书写代码的可读性 可修改性 可重用性 优化代码综合和仿真的结 果 指导设计工程师使用VerilogHDL规范代码和优化电路 规范化公司的ASIC设计输入从而做到

- 逻辑功能正确

- 可快速仿真

- 综合结果最优( 如果是hardware model)

- 可读性较好

2 范围

本规范涉及Verilog HDL编码风格 编码中应注意的问题 Testbench的编码等本规范适用于Verilog model的任何一级 RTL ehavioral, gate_level) 也适用于出于仿真综合或二者结合的目的而设计的模块

3 定义

- Verilog HDL :Verilog 硬件描述语言

- FSM :有限状态机

- 伪路径 : 静态时序分析 STA 认为是时序失败 而设计者认为是正确的路径。

4 引用标准和参考资料

下列标准包含的条文 通过在本标准中引用而构成本标准的条文 在标准出版时 所示版本均为有效 所有标准都会被修订 使用本标准的各方应探讨 使用下列标准最新版本的可能性。

5规范内容

5.1 Verilog 编码风格

本章节中提到的Verilog编码规则和建议适应于 Verilog model的任何一级 RTL behavioral,gate_level) 也适用于出于仿真 综合或二者结合的目的而设计的模块

5.1.1

选择有意义的信号和变量名 对设计是十分重要的 命名包含信号或变量诸如出处 有效状态等基本含义 下面给出一些命名的规则

- 用有意义而有效的名字 有效的命名有时并不是要求将功能描述出来 如:

For ( I = 0; I < 1024; I = I + 1 )

Mem[I] <= #1 32’b0;

For 语句中的循环指针I 就没必要用loop_index作为指针名

-

用连贯的缩写 长的名字对书写和记忆会带来不便 甚至带来错误 采用缩写时应注意同一信号在模块中的一致性 缩写的例子如下

Addr

:address

Pntr

:pointer

Clk

:clock

Rst

:reset

-

用最右边的字符下划线表示低电平有效 高电平有效的信号不得以下划线表示 短暂 的引擎信号建议采用高有效 如

Rst_ Trdy_, Irdy_ Idsel.

-

大小写原则 名字一般首字符大写 其余小写 但parameter, integer 定义的数值名可全部用大写两个词之间要用下划线连接。 如

Packet_addr, Data_in, Mem_wr Mem_ce_

-

全局信号名字中应包含信号来源的一些信息 如 D_addr[7:2] 这里的 D 指明了地址是解码模块(Decoder module)中的地址

-

同一信号在不同层次应保持一致性

-

自己定义的常数 类型等用大写标识 如 parameter CYCLE=100

-

避免使用保留字 如 in out x z等不能够做为变量 端口或模块名

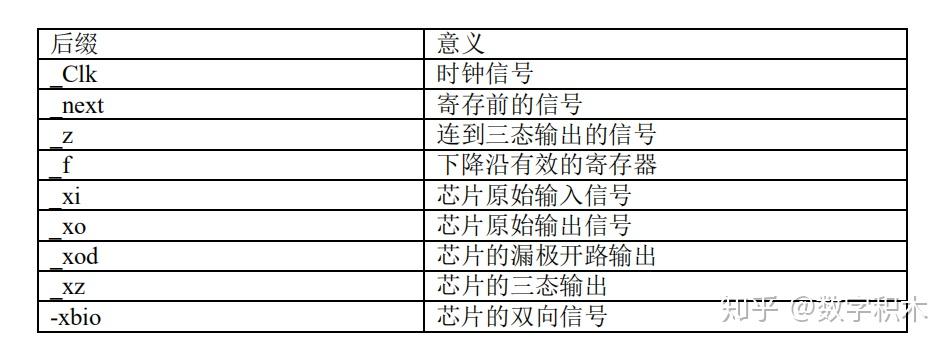

- 添加有意义的后缀 使信号名更加明确 常用的后缀如下:

5.1.2 Modules

-

顶层模块应只是内部模块间的互连 Verilog设计一般都是层次型的设计 也就是在设计中会出现一个或多个模块 模块间的调用在所难免 可把设计比喻成树 被调用的模块就是树叶 没被调用的模块就是树根 那么在这个树根模块中 除了内部的互连和模块的调用外 尽量避免再做逻辑 如不能再出现对reg变量赋值等 这样做的目的是为了更有效的综合 因为在顶层模块中出现中间逻辑 Synopsys 的design compiler 就不能把子模块中的逻辑综合到最优。

-

每一个模块应在开始处注明文件名 功能描述 引用模块 设计者 设计时间及版权信息等,如:

Filename ﹕ RX_MUX.v

Author ﹕

Description ﹕

Called by ﹕Top module

Revision History ﹕99-08-01

Revision 1.0

Email ﹕ M@sz.huawei.com.cn

Company ﹕ Huawei Technology .Inc

- 不要对Inpu t进行驱动, 在module 内不要存在没有驱动的信号 更不能在模块端口中出现没有驱动的输出信号,避免在仿真或综合时产生warning 干扰错误定位。

-

每行应限制在80个字符以内 以保持代码的清晰 美观和层次感 一条语句占用一行 如果较长 超出80个字符 则要换行

-

电路中调用的 module名 用 Uxx 标 示 向量大小表 示要清晰 采用基于名字(name_based )的调用而非基于顺序的 (order_based),如:

Instance UInstance2(

.DataOut (DOUT ),

.DataIn (DIN ),

.Cs_ (Cs_ )

-

用一个时钟的上沿或下沿采样信号, 不能一会儿用上沿 ,一会儿用下沿 ,如果既要用上沿又要用下沿 ,则应分成两个模块设计。 建议在顶层模块中对Clock做一非门,在层次模块中如果要用时钟下沿就可以用非门产生的Posedge Clk_, 这样的好处是在整个设计中采用同一种时钟沿触发, 有利于综合。基于时钟的综合策略

-

在模块中增加注释 对信号 参量 引脚 模块 函数及进程等加以说明 便于阅读与维护

-

Module 名要用大写标示 且应与文件名保持一致, 如

Module DFF_ASYNC_RST(